在半导体器件中,欧姆接触是连接内部有源区与外部电路或其他器件的生命线,其性能优劣直接关系到整个器件的电学表现。从物理学家或工程师的视角来看,一个理想的欧姆接触应具备以下特征:

然而,在实际的金属-半导体界面上,完美的欧姆接触并非天然形成。功函数差异与界面态的存在,往往会形成一个能量壁垒,即肖特基势垒。如何让电子高效地跨越这道“鸿沟”,是实现低电阻欧姆接触的核心挑战。

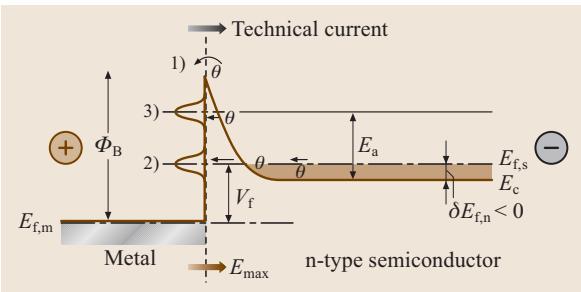

当金属薄膜(例如通过蒸发工艺)沉积在n型半导体上时,若两者功函数与电子亲和能匹配不佳,便会在半导体一侧形成势垒高度为 ΦB 的阻碍。即使精心选择材料体系,一个或大或小的势垒在多数情况下也难以避免。电子要想从半导体进入金属,必须克服或穿透这个势垒。其主要路径可归纳为以下三种电流传导机制。

图1. 高掺杂简并n型半导体与金属接触在正向偏压下的能带图(金属电位高于接地的n型半导体)

热电子发射 (Thermal Emission):电子依靠自身的热能(与kT相当)来“翻越”高度近似为 ΦB 的势垒。只有少数高能电子能够成功越过,因此这种机制效率低下,形成的接触电阻很大,在室温下常表现出明显的整流特性。顾名思义,该过程对温度高度敏感,在高温下呈指数级增强。

场致发射或隧穿 (Field Emission or Tunneling):这是一种纯粹的量子力学现象。当半导体掺杂浓度极高(远超 1018 cm-3)时,界面处的空间电荷区会变得极窄(小于10 nm)。如果势垒宽度小于电子的德布罗意波长,电子便能利用其波动性,在不损失能量的情况下直接“穿透”势垒。该过程几乎与温度无关,即便在极低温下也同样有效,因为量子隧穿无需热能激活。

热场发射 (Thermal Field Emission):此机制介于上述两者之间,常见于中等掺杂水平的半导体。一部分电子先被热能激活到一个较高的能级,虽然能量仍不足以越过势垒顶峰,但在此位置,它们需要隧穿的势垒变得更窄、更低。与纯粹的热发射或场致发射相比,电子面对的是一个等效上更易穿越的障碍。可以看作是热激发与隧穿两种机制的串联协作。

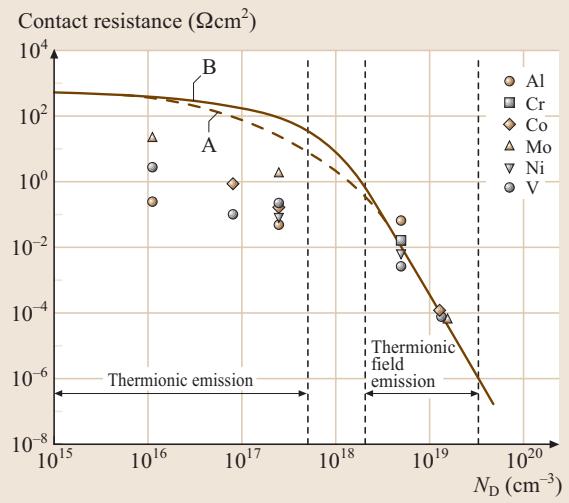

图2. 不同金属在n型硅上的接触电阻与硅掺杂浓度ND的关系

上图清晰地展示了掺杂浓度对接触电阻(单位:Ω·cm2)的决定性影响。随着掺杂浓度提升,电流传导机制逐渐从热电子发射过渡到场致发射(隧穿),接触电阻急剧下降。在工程应用中,接触电阻率通常要求低于 10-5 Ω·cm2。为达到此目标,掺杂浓度需要超过 1019 cm-3,以确保隧穿效应占据绝对主导。目前,先进工艺已能实现低于 10-7 Ω·cm2 的接触电阻率。

在讨论接触电阻时,有必要精确区分两个概念:

根据电流扩展方式,接触可分为两类:

相应的,接触电阻的测量技术也需根据接触的几何构型来选择。测量的核心目标是从数值通常偏高的总接触电阻中,精确地提取出数值较低的比接触电阻,从而为优化接触工艺(如退火)提供可靠依据。

开尔文结构 (Kelvin Configuration) 测量欧姆接触时,普遍采用开尔文结构(即四探针法)来消除测量探针与接触焊盘之间附加电阻带来的误差。其原理是使用两根探针施加恒定电流,再用另外两根独立的探针在尽可能靠近待测区域的位置测量电压。

Cox & Strack 方法 对于电流近乎均匀流入的垂直接触,可以采用Cox和Strack提出的方法。该方法通过在半导体上制作一系列不同直径的圆形接触点,来区分比接触电阻和扩展电阻的贡献。

传输线模型 (Transmission Line Model, TLM) 对于电流非均匀流动的横向接触(尤其是在薄半导体层上),由Berger提出的传输线模型(TLM)是一种功能更强大、应用更广泛的方法。

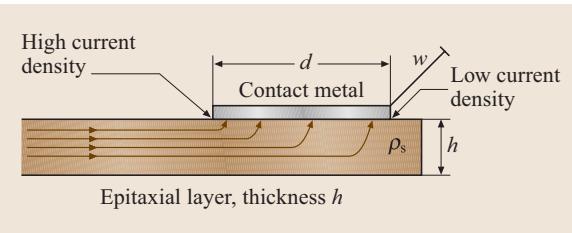

图3. 宽度为w、长度为d的横向接触在厚度为h的薄外延层上的电流分布示意图

如图3所示,电流在横向接触下的分布是复杂的。假设半导体薄层具有电阻率 ρs (Ω·cm) 和薄层电阻 Rs (Ω/□),其中 Rs = ρs / h。在实际器件中,薄层厚度 h 通常远小于接触长度 d。

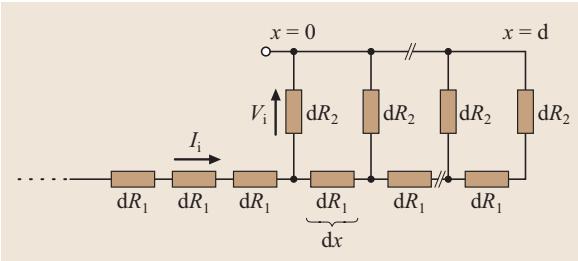

图4. 基于图3电流分布的横向欧姆接触等效电路图

这种结构可以等效为一个传输线网络(图4)。外延层的电阻由一系列差分单元 dR1 串联而成,而比接触电阻 ρc 则由分布式的垂直单元 dR2 代表。总接触电阻 Rc 定义为接触区域起始端的电压与流入结构的总电流 I 之比。

图5. 用于提取薄层电阻Rs和总接触电阻Rc的TLM测试结构掩模版

为了从测得的总接触电阻 Rc 中提取出比接触电阻 ρc,需要求解描述该传输线模型的微分方程,最终得到一个隐式方程:

$$ R_{/mathrm{c}} = /frac{1}{w}/sqrt{/left[R_{/mathrm{s}}/left(/rho_{/mathrm{c}} + 0.2R_{/mathrm{s}}h^{2}/right)/right]} /times /coth /left(/sqrt{/frac{R_{/mathrm{s}}}{/left(/rho_{/mathrm{c}} + 0.2R_{/mathrm{s}}h^{2}/right)}} d/right) $$

要解出此方程中的 ρc,必须先测得 Rc 和 Rs,并精确获知测试结构的几何常数 w、h 和 d。

Rs 和 Rc 的测量可以通过一个包含多个接触条的TLM测试结构(图5)来完成。通常需要进行两次开尔文测量:

通过这两个电压值 V1、V2 和恒定电流 I,可以计算出薄层电阻 Rs 和每个接触条下方的总接触电阻 Rc:

$$ R_{/mathrm{s}} = /frac{V_1 - V_2}{l_1 - l_2}/frac{w}{I} $$

$$ R_{/mathrm{c}} = /frac{1}{2}/left(/frac{V_1}{I} -l_1/frac{R_{/mathrm{s}}}{w}/right) $$

获得 Rs 和 Rc 后,即可代入前述的隐式方程求解比接触电阻 ρc。值得强调的是,接触间距 l1 和 l2 (通常在 1-100 μm 范围) 必须进行高精度测量(亚微米级),否则会给 ρc 的计算带来巨大误差,尤其是当 ρc 低于 10-6 Ω·cm2 时。因此,要获得可靠的接触电阻数据,对测试结构的加工精度和测量手段都有极高要求。这正是专业检测实验室的核心价值所在。

精工博研测试技术(河南)有限公司(原郑州三磨所国家磨料磨具质量检验检测中心),央企,国字头检测机构,专业的权威第三方检测机构,专业检测半导体电学性能,可靠准确。欢迎沟通交流,电话19939716636

对于电学长接触(例如 d = 40 μm),可以定义两个重要的衍生参数:

传输长度 (Transfer Length, LT):定义为 LT = √(ρc / Rs)。它形象地描述了电流从半导体外延层“传输”进入金属接触所需的典型长度。在实际设计中,接触电极的长度没有必要超过三倍传输长度,因为更长的部分对降低接触电阻的贡献已微乎其微。

传输电阻 (Transfer Resistance, RT):定义为 RT = √(Rsρc) (Ω·mm)。该参数表征了对于给定宽度 w 的电学长接触,所能达到的最低接触电阻。例如,对于场效应晶体管(FETs),其传输电阻值应低于 0.2 Ω·mm。

这两个参数将微观的材料特性(ρc, Rs)与宏观的器件设计(接触长度、总电阻)联系起来,为器件工程师提供了直观且实用的设计指引。

首页

首页

检测领域

检测领域

服务项目

服务项目

咨询报价

咨询报价